Mahasiswa STEI ITB Juara Lomba Perancangan Chip pada Ajang SEACAS CHIPATON 2023

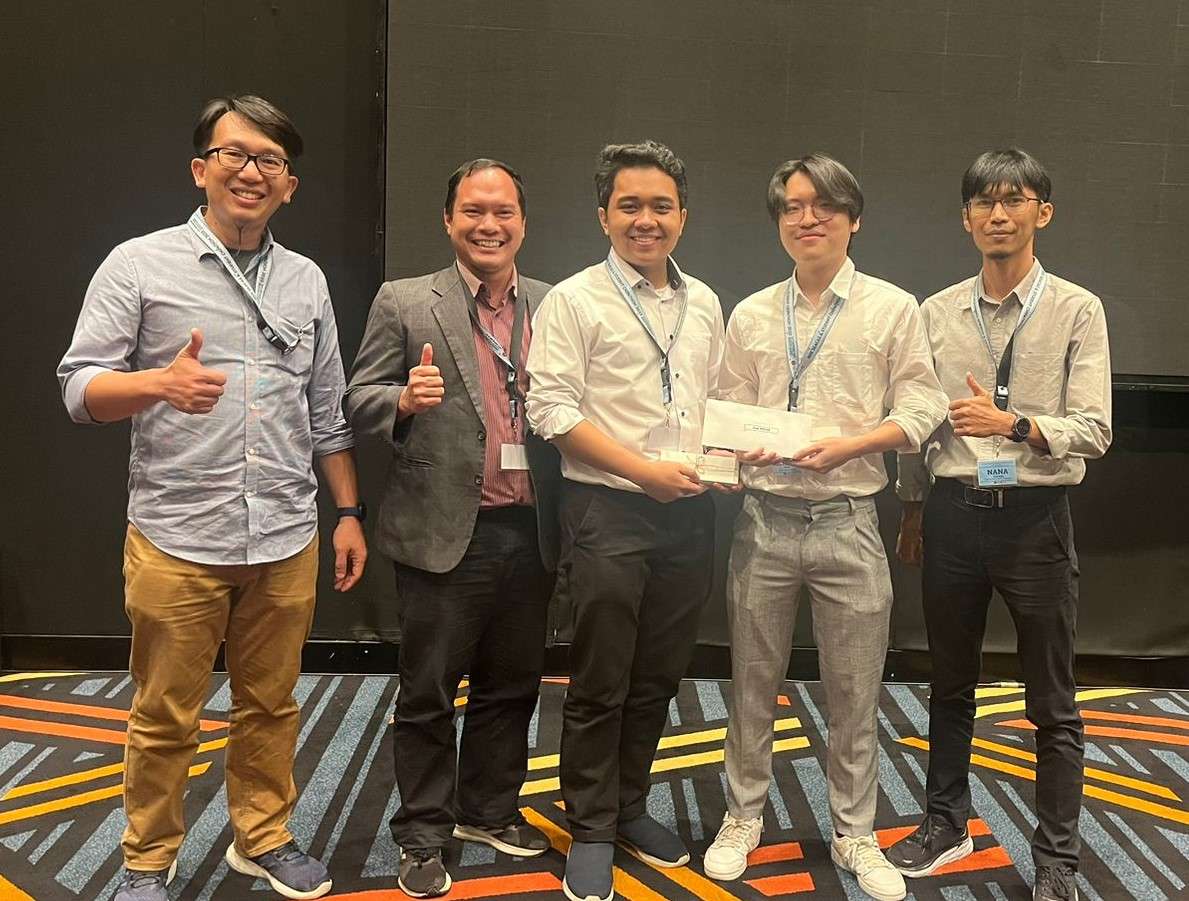

Bandung, stei.itb.ac.id – Tim mahasiswa dari Sekolah Teknik Elektro dan Informatika ITB yang diwakili oleh dua mahasiswa Program Studi Teknik Elektro, Fauzan Ibrahim dan Nicholas Teffandi meraih Penghargaan second winner dalam ajang lomba perancangan chip Internasional, South East Asia Circuit and System Society (SEACAS) and Student Chipaton 2023. Ajang tahunan ini diselenggarkan oleh IEEE CAS Chapter, di mana pada tahun 2023 diadakan di University of Philippines Diliman pada tanggal 18-19 September 2023. Perlombaan ini diikuti oleh peserta dari 6 negara ASEAN, yaitu Indonesia, Singapura, Malaysia, Thailand, Vietnam, Philiphina, dan Jepang.

Pada lomba tahun ini, topik perlombaan adalah mengenai perancangan modul Fast Fourier Transform (FFT), yang merupakan salah satu modul pemroses sinyal digital yang banyak dimafaatkan dalam sistem komunikasi nirkabel (wireless communication), pemrosesan citra (image processing) maupun pengolah suara (audio processing), dll.

Pada lomba ini, peserta diminta untuk melakukan optimasi dan implementasi rangkaian dasar FFT 16-point dalam bentuk layout chip. Kriteria penilaian untuk menentukan pemenang adalah: (1) Ketercapaian kinerja sistem dalam hal kecepatan komputasi, luas area dan tingkat konsumsi daya. Parameter kinerja ini diukur dalam Figure of Merit (FoM) yang sekecil mungkin; (2) Inovasi rancangan, yakni kebaharuan atau advantage rancangan sistem dibandingkan dengan rancangan dasar yang diberikan sebagai rangkaian pembanding; (3) Metodologi Perancangan yang sistematis dan (4) Presentasi akhir rancangan.

Tim mahasiswa STEI dalam lomba ini mengusulkan rancangan FFT dengan arsitektur parallel radix-4 sehingga memungkinkan waktu komputasi FFT dapat dilakukan lebih cepat. Selain optimasi dalam level arsitektur VLSI, tim dari STEI juga mengusulkan optimasi dalam tahap implementasi chip, yakni dengan melakukan otimasi dalam proses floor planning dan placement-and-routing. Optimasi ini menghasilkan kerapatan logic cell chip yang cukup tinggi sehingga luas area chip menjadi lebih kecil, yang akan berkorespondensi juga degan konsumsi daya yang lebih rendah. Selama persiapan dan pelaksanaan lomba, tim mahasiswa dari STEI mendapat bimbingan dan pendampingan oleh tim dosen Kelompok Keahlian Elektronika yaitu Nana Sutisna, Ph.D dan Dr. Eng. Infall Syafalni.

Dalam proses penjurian, penilaian rancangan chip dilakukan oleh tim juri yang terdiri dari perwakilan CAS Chapter Setiap negara dan IEEE ISCAS committee (General Chair dan TPC Chair). Pada presentasi akhir, tim dari STEI merupakan satu dari dua tim yang berhasil mengimplementasikan rancangan hingga tahap chip layout. Hasil tersebut dapat meyakinkan dewan Juri dan terpilih sebagai peringkat kedua.

Sumber : Nana Sutisna, Ph.D